The use of FPGAs is more extensive than we usually imagined, because there are more types of modules integrated, not just the original Simple Logic Unit (LE). Early FPGAs were relatively simple. All functional units were built only by pins, internal buffers, LEs, and RAM. LEs consisted of LUTs (lookup tables) and D flip-flops. RAM also had very small capacity. Today's FPGAs not only include the previous LE, but also larger, faster, and more flexible RAM. The IOB is more complex, supports more IO types, and integrates some special functional units, including: DSP: In fact, it is a multiplier, FPGA can integrate multiple multipliers, and the general DSP chip often has only one core per core. In other words, FPGAs can more easily implement multiple DSP core functions. In some cases where a large number of multiply-accumulate calculations are required, it is often the case that multiple multipliers work in parallel at a speed far exceeding a high speed multiplier. SERDES: High speed serial interface. In the future, there will be more and more high-speed serial interfaces such as PCI-E, XAUI, HT, and S-ATA. With the SERDES module, FPGAs can easily integrate these high-speed serial interfaces without the need to purchase a dedicated interface chip. CPU core: divided into 2 types, soft core and hard core. Soft core is a CPU module written in logic code that can be implemented in any FPGA with sufficient resources and is very flexible to use. Moreover, multiple soft cores can be integrated in a large-capacity FPGA to achieve multi-core parallel processing. The hard core is a CPU core that is built inside a specific FPGA. The advantage is that the speed is fast and the performance is good. The disadvantage is that it is not flexible enough. However, FPGAs still have drawbacks. For some high-frequency applications, FPGAs can't do anything about it. Although theoretically FPGA can support 500MHz, in actual design, often the operating frequency above 200MHz is difficult to achieve. One of the key points of FPGA design: clock tree For FPGAs, avoid asynchronous design as much as possible and use synchronous design whenever possible. The first key to synchronous design, and the key to the key, is the clock tree. A bad clock tree is an irreparable disaster for FPGA design. It is a building without a good foundation. The collapse is inevitable. Specific design details: 1) Use a single clock whenever possible; 2) If there are multiple clock domains, be sure to carefully divide them, be careful; 3) Signals across the clock domain must be synchronized. For control signals, double sampling can be used; for data signals, asynchronous fifo can be used. It should be noted that asynchronous fifo is not a panacea, an asynchronous fifo can only solve the frequency difference problem within a certain range. 4) Use the PLL and DLL inside the FPGA as much as possible, which will bring a lot of benefits to your design. 5) For special IO interfaces, you need to carefully calculate Tsu, Tco, Th, and use a variety of tools such as PLL, DLL, DDIO, and the delay that can be set by the pin. Simply constraining the pins with Tsu, Tco, and Th is often not possible. What may be said is not very accurate. The clock tree here actually refers to the clock scheme, mainly the planning of the clock domain and the PLL. Generally, the detailed calculation of the trace delay is not involved (generally, the global clock network and the local clock network are fixed, and the delay is fixed). , and the clock tree in the ASIC is not the same. For ASICs, careful analysis and calculation of the design, routing, and delay calculation of the clock network is required. The second point of FPGA design: FSM FSM: finite state machine. This can be said to be the basis of logical design. Almost a little larger logic design can almost see FSM. The FSM is divided into a moore type and a merly type. The state transition of the moore type is independent of the variable, and the merly type is related. Most of the actual use is merly type. FSM usually has two ways of writing: single process, dual process. Beginners tend to prefer single-process writing in the following format: Always @( posedge clk or posedge rst ) Begin If ( rst == 1'b1 ) FSM_status <<= . . . . . . ; Else Case ( FSM_status ) . . . . . . ; Endcase End Simply put, a single-process FSM puts all synchronous and asynchronous processing into one always. The third point of FPGA design: latch First answer: 1) stateCAD has not been used, but I feel that it is not very convenient to use this stuff to build a large system. Maybe better with system C or system Verilog. 2) Synchronous and asynchronous calling is the customary name of my company. It is not right, but I am used to it, huh, huh. Tell me about the latch this time. The hazard of the latch has already been said. I won’t say more here. The key is how to avoid it. 1) In the combination logic process, the if statement must have else! And all signals are assigned in all branches of if. Always @( * ) begin If ( sig_a == 1'b1 ) sig_b = sig_c; End This is definitely a latch. The correct one should be Always @( * ) begin If ( sig_a == 1'b1 ) sig_b = sig_c; Else sig_b = sig_d; End Also note that the following will also generate a latch. In other words, in the process of combinatorial logic, you cannot assign yourself to yourself or indirectly to yourself. Always @( * ) begin If ( rst == 1'b1 ) counter = 32'h00000000; Else counter = counter + 1; End But if it is a sequential logic process, then there is no such problem. 2) The default of the case statement must not be less! The reason is the same as the if statement, so I won’t say more here. Need to be reminded that in the sequential logic process, the default statement must also be added, this is a good habit. 3) Combinational logic process sensitive variables can not be less or more. This problem is not too big, verilog2001 syntax can be directly used * to get it. By the way, it is definitely beneficial to have a disadvantage. In the LE of the FPGA, there is always a latch and a D flip-flop. There is also a latch in the IOE (IOB) that supports DDR to implement DDIO. However, in our usual design, it is still necessary to respect the latch as far as possible. The fourth point of FPGA design: logic simulation Simulation is an indispensable step in FPGA design. Without simulation, there is nothing. Simulation is a monotonous and tedious task, and it is easy to create the idea of ​​giving up or cutting corners. Be sure to hold on! The simulation is divided into unit simulation, integrated simulation, and system simulation. Unit Simulation: Simulation for each of the smallest basic modules. Unit simulation requires code line coverage, conditional branch coverage, and expression coverage to be 100%! All three coverages can be viewed through MODELSIM, but need to be set in Compile opTIon when compiling the module. Integrated simulation: Combine multiple large modules for simulation. Coverage requirements are as high as possible. System Simulation: Combine the entire hardware system for simulation. At this point, the entire simulation platform includes the simulation model of the logic peripheral chip interface, as well as BFM, Testbench and so on. The system simulation needs to carefully design the simulation test case and the simulation test platform according to the function and performance requirements of the simulated logic. System simulation is a big branch of logical design and a discipline that requires special learning. Matte Hydrogel Screen Protector

The anti-glare technology used in the Matte Protective Film can reduce glare to eliminate eye fatigue, and make it easier to watch under direct light, which is more friendly to your eyes.

In order to let you enjoy it for a long time, the Frosted Screen Protector uses durable military-grade TPU material, which has strong durability and scratch resistance. It protects the screen from unnecessary scratches.

It has good anti-fingerprint ability, sweat will not remain on the screen surface, and it is easy to clean without affecting touch sensitivity or response speed.

The adhesive layer ensures that you stick the Protective Film in a stress-free manner and maintain a strong adhesion without leaving any sticky residue.

If you want to know more about Matte Screen Protector products, please click the product details to view the parameters, models, pictures, prices and other information about Matte Screen Protector.

Whether you are a group or an individual, we will try our best to provide you with accurate and comprehensive information about the Matte Screen Protector!

Matte Screen Protector, Frosted Screen Protector, Matt Screen Protector, Matte Hydrogel Film, Matt Protective Film, Anti-Glare Screen Protector Shenzhen Jianjiantong Technology Co., Ltd. , https://www.jjthydrogelmachine.com

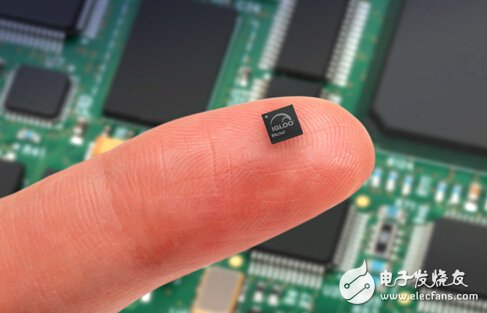

FPGA application