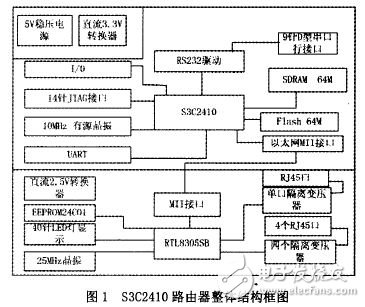

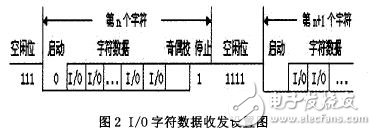

0 Preface It is predicted that the global router market will reach $15.9 billion by 2015. Among them, the development of home routers is particularly rapid. The regions with the greatest demand are North America and Europe, but the Asian region has become the fastest growing region in the home router market. So in the next few years, the demand for home routers in Asia will be huge. Traditional routers will continue to exist in the market for a period of time due to their low price, but the development trend of routers is intelligent and networked. This is the characteristic of routers represented by ARM and MIPS cores, so ARM core routers will be In the near future, it will occupy a place in the home router market, and with the popularity of ARM core technology, ARM core routers will have higher cost performance, and will be more competitive than other home routers. 1 ARM technology ARM does not produce chips or sell chips, it only sells chip technology licenses. The main technologies of embedded ARM include: ARM processor architecture and ARM processor instruction set, storage system and abnormal interrupt processing. (1) ARM architecture: With the addition of the T variant, the processor state can be switched to the Thumb state, in which the instruction set is a 16-bit Thumb instruction set. (2) ARM processor instruction set: ARM instruction set can be divided into jump instruction, data processing instruction, program status register transfer instruction, Load/Store instruction, coprocessor instruction and abnormal interrupt generation instruction 6 [1]. (3) ARM storage system: The architecture of the ARM storage system adapts to the needs of different embedded application systems. The simplest storage system uses a flat-panel address mapping mechanism. As in some simple microcontroller systems, the address space is allocated in a fixed manner, and all parts of the system use physical addresses. Some complex systems may include one or more of the following technologies to provide a more powerful storage system. (4) Abnormal interrupt: When an abnormal interrupt occurs, the system will jump to the corresponding abnormal interrupt execution after executing the current instruction. When the abnormal interrupt routine is executed, the program returns to the next instruction of the instruction that generated the interrupt. 2 router (1) Central processor: The CPU of the router is responsible for the configuration management of the router and the forwarding of data packets, such as various tables and routing operations required to maintain the router. The processing speed of a router for a packet depends largely on the type and performance of the CPU. (2) Memory: The router can use a variety of memory, ROM (read-only), Flash (flash), DRAM (dynamic). (3) Interface: The physical connection between the router and various different networks must be implemented through the interface. The more high-end routers, the more types of networks that can be connected, the more types of interfaces they have. (4) Console port: According to the type of router, the specific interface mode for connecting with the console is different. There are two common types: the console port of DB-25 and the console port of RJ-45. 3 S3C2410 router design (1) Overall structure diagram The overall structural block diagram of the home S3C2410 router designed in this paper is shown in Figure 1. (2) Main function realization (1) I/0 part 1) Port Configurator (GPACON'GPHCON) In the S3C2410, most of the pins are multiplexed. Therefore, define a function for each pin requirement. The port controller (GPnCON) defines the function of each pin (n=A'H). If GPFO'GPF7 and GPG0'GPG7 are used as wake-up signals in power-down mode, these port configurations must be set in interrupt mode. 2) Port Data Register (GPADAT'GPHDAT) If the port is configured as an output port, data can be written to the corresponding bit in the GPnDAT register. If the port is configured as an input port, data can be read from the corresponding bit in the GPnDAT register. 3) The port pull-up register (GPBUP 'GPHUP) port pull-up register controls the enable or disable of the pull-up register of each port group. When the corresponding bit is 0, the pull-up register of this pin is enabled; when it is 1, the pull-up register is disabled. 1) Data transmission operations These can be set by the linear controller (uLCONn). 2) Data reception: They are all set by a linear controller (ULCONn). 3) Baud Rate Generator: The baud rate is determined by the 16-bit divisor specified by the clock source (PCLK or UCLK) divided by 16 and the UART Baud Rate Divisor Register (UBRDIVn). (3) Storage device components Compared with Flash memory, SDRAM does not have the characteristics of power-down and data retention, but its storage speed is much higher than that of Flash memory and has read/write properties. Therefore, SDRAM is mainly used in the system for the operation of space, data and stack. When the system starts, the CPU first reads the startup code from the reset address OxO. After the initialization of the system is completed, the program code is transferred to the SDRAM to run, so as to improve the running speed of the system. NAND Flash and NOR Flash: NOR and NAND are the two main non-volatile flash technologies on the market today. The NOR features on-chip execution (XIP, eXecute In Place) so that applications can run directly in the flash memory without having to read the code into system RAM. The transmission efficiency of NOR is very high, and it is very cost-effective in a small capacity of l~4MB, but the low write and erase speed greatly affects its performance. The NAND structure provides extremely high cell density, high memory density, and fast write and erase speeds. The difficulty in applying NAND lies in the management of Flash and the need for special system interfaces. Performance comparison: â—NOR reads slightly faster than NAND. â— NAND write speed is much faster than NOR. â— NAND's 4ms erase speed is much faster than NOR's 5s. â— Most write operations require an erase operation first. The NAND erase unit is smaller and the corresponding erase circuit is less. 4 summary The S3C2410 router has 64M SDRAM and an operating frequency of up to 203MHz, which can be used to port mainstream embedded operating systems. Manufacturers can add wireless modules and software to add hardware and software according to the needs of different users. Regardless of hardware or software, S3C2410 routers have very strong performance advantages compared with mainstream home routers on the market. With the continuous reform of network facilities, the transmission speed of the network will continue to accelerate. At the same time, with the integration of the network, the network security problem is gradually highlighted, and the stability of the operating system of the router and the firewall on it have higher requirements. Therefore, these changes will result in higher and higher requirements for the load capacity and information processing capability of the router, so that the advantages of the S3C2410 router will become more obvious. The design of the 83C2410 router complies with the development requirements of the router market, and can meet the requirements of network development for information processing and security of routers, and has certain theoretical and practical value. Home Air Purifier,Air Purifier,Room Air Purifier,Indoor Air Purifier CIXI KYFEN ELECTRONICS CO.,LTD, , https://www.kyfengroup.com